Analog Devices Inc. AD9546 Digitalisierter Dual-DPLL-Taktsynchronisator

Der Analog Devices Inc. AD9546 digitalisierte Dual-DPLL-Taktsynchronisator kombiniert eine digitalisierte Takttechnologie, die Taktsignale in Systemen überträgt und verteilt. Die digitalisierte Taktung auf dem AD9546 ermöglicht das Design von flexiblen und skalierbaren Takttransportsystemen mit gut geregelter Phasenausrichtung (Zeit). Der AD9546 eignet sich hervorragend für das Design von Netzwerkanlagen, welche die Synchronisierungsanforderungen für IEEE® 1588™ Grenztakte gemäß ITU-T G.8273.2 Klasse D erfüllen müssen. Darüber hinaus ist die digitalisierte Taktung auch in Applikationen relevant, die den genauen Transport von Frequenz und Phase zu mehreren Nutzungs-Endpunkten erfordern, wie z. B. die Verteilung von synchronisierten Systemreferenztakten (SYSREF) auf ein Array von ADC-Kanälen.Der AD9546 digitalisierte Dual-DPLL-Taktsynchronisator unterstützt bestehende und sich abzeichnende internationale Telekommunikationsstandards (ITU-T G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825 und ITU-T G.8273.2.

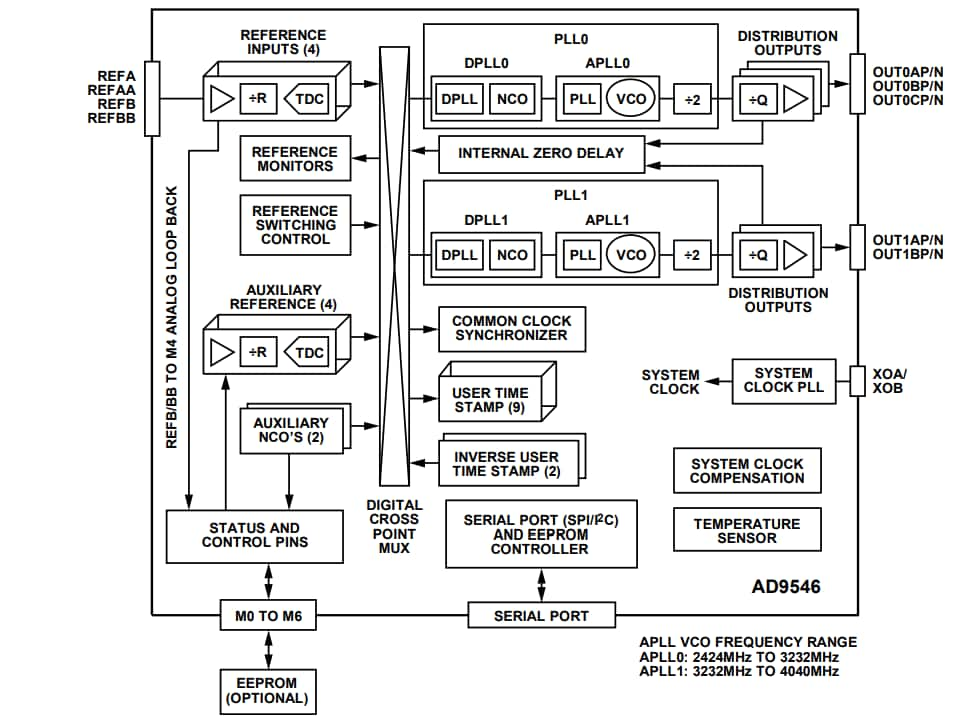

Das Bauteil bietet zehn Taktausgänge, die mit einer von bis zu acht Eingangsreferenzen synchronisiert werden. Die digitalen Phasenregelschleifen (DPLLs) reduzieren den Timing-Jitter, der mit den externen Referenzen verbunden ist, und die analogen Phasenregelschleifen (APLLs) bieten eine Frequenzumsetzung mit Ausgangstakten mit geringem Jitter. Die digital gesteuerte Schleifen- und Holdover-Schaltungen erzeugen einen konstanten Ausgangstakt mit geringem Jitter selbst dann, wenn alle Referenzeingänge versagen.

Der AD9546 ist in einem 48-Pin-LFCSP-Gehäuse (7 mm × 7 mm) untergebracht und wird über einen Temperaturbereich von -40 °C bis +85 °C betrieben.

Merkmale

- Digitalisiertes Takttransport-Subsystem

- 9 unabhängige UTS-Blöcke (Zeitstempel-Ausgangsanschlüsse)

- 2 unabhängige IUTS-Blöcke (Zeitstempel-Eingangsanschlüsse)

- Die duale DPLL synchronisiert einen physikalischen Schichttakt von 1 Hz bis 750 MHz und bietet eine Frequenzumsetzung mit Jitter-Reinigung von störenden Referenzen.

- Erfüllt die Anforderungen von ITU-T G.8262 und Telcordia GR-253

- Unterstützt Telcordia GR-1244, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825 und ITU-T G.8273.2

- Kontinuierliche Frequenzüberwachung und Referenzvalidierung für Frequenzabweichung so niedrig wie 50 ppb (5 × 10−8)

- Beide DPLLs verfügen über einen 24-Bit-Fractional-Teiler mit einem programmierbaren 24-Bit-Modul

- Programmierbare digitale Schleifenfilterbandbreite: 0,0001 Hz bis 1.850 Hz

- 2 unabhängige, programmierbare Hilfs-NCOs (1 Hz bis 65.535 Hz, Auflösung < 1,37 pHz), geeignet für IEEE 1588

- Servo-Feedback der Version 2 in PTP-Applikationen

- Automatische und manuelle Holdover- und Referenz-Umschaltung bietet einen berührungslosen Betrieb mit Nullverzögerung oder einen phasenversetzten Betrieb

- Programmierbare auf der Priorität basierte Referenzschaltung mit Unterstützung für manuelle, automatische Rückmelde- und automatische Nichtrückmelde-Modi.

- Fünf Taktausgangs-Pinpaare, wobei jedes Paar als Differential-LVDS-/HCSL-/CML- oder als zwei einendige Ausgänge einsetzbar ist (1 Hz bis 500 MHz)

- Zwei differenzielle oder acht einendige Eingangsreferenzen

- Kreuzpunkt-MUX verbindet Referenzeingänge zu PLLs

- Unterstützt embedded (modulierte) Eingangs-/Ausgangs-Taktsignale

- Schnelle DPLL-Verriegelungsmodi

- Bietet eine interne Funktion, um das niedrige Phasenrauschen eines Quarzresonators oder Quarzoszillators mit der Frequenzstabilität und der

- Genauigkeit eines TCXO oder OCXO zu kombinieren

- Externe EEPROM-Unterstützung für autonome Initialisierung

- 1,8 V Einzelversorgungsbetrieb mit interner Regelung

- Integrierte Temperaturüberwachung sowie Alarm- und Temperaturkompensation für eine verbesserte Nullverzögerungsleistung

Applikationen

- Synchronisierung mit hoher Genauigkeit und 5-G-Timing-Transport

- Globales Positionierungssystem (GPS), Präzisions-Zeitprotokoll (PTP) (IEEE 1588) und synchrone Ethernet(SyncE)-Jitter-Bereinigung und -Synchronisierung

- Optische Transportnetzwerke (OTN), synchrone digirale Hirarchie (SDH) sowie Makro- und Kleinzellen-Basisstationen

- Taktung von kleinen Basisstationen (Basisband und Funk)

- Stratum 2, Stratum 3e und Stratum 3 Holdover, Jitter-Bereinigung und Phasenübergangssteuerung

- JESD204B-Unterstützung für Taktung eines Analog-Digital-Wandlers (ADC) und Digital-Analog-Wandlers (DAC)

- Carrier-Ethernet

Blockdiagramm