Zilog / IXYS Z8xC30 CMOS-Controller für serielle Kommunikation

Zilog/IXYS Z8xC30 CMOS-Controller für serielle Kommunikation (SCCs) haben einen geringen Stromverbrauch, eine höhere Leistungsfähigkeit und eine hervorragende Rauschimmunität. Diese SCCs umfassen Z85C30 SCCs, die für MCUs ohne Multiplex-Bus optimiert sind, Z80C30 SCCs, die für Multiplex-Bus-MCUs optimiert sind und Z84C30 Zähler-/Timer-Schaltungen (CTCs). Die Z80C30/Z85C30 SCCs sind Zweikanal-Multiprotokoll-Datenkommunikationsperipherien, die sich einfach mit CPUs verbinden lassen. Zusätzliche Funktionen umfassen einen 10x19-Bit-Status-FIFO und einen 14-Bit-Byte-Zähler zur Unterstützung von Hochgeschwindigkeits-SDLC-Übertragungen mit DMA-Controllern. Durch die flexible Programmierung der internen Register können die SCCs für verschiedene serielle Kommunikationsanwendungen konfiguriert werden.Merkmale

- Z85C30: optimiert für Mikroprozessoren mit nicht gemultiplextem Bus

- Z80C30: optimiert für Mikroprozessoren mit Multiplex-Bus

- Pin-kompatibel zu NMOS-Versionen

- Zwei unabhängige Vollduplex-Kanäle von 0 bis 4,1 Mbit/s, jeder mit eigenem Quarzoszillator, Baudratengenerator (BRG) und digitalem Phasenregelkreis (DPLL) zur Taktrückgewinnung

- Multiprotokollbetrieb unter Programmsteuerung; programmierbar für NRZ-, NRZI- oder FM-Datenkodierung

- Asynchroner Modus mit 5 bis 8 Bits und 1, 1½ oder 2 Stoppbits pro Zeichen, programmierbarer Taktfaktor, Erkennung und Erzeugung von Unterbrechungen, Erkennung von Paritäts-, Überlauf- und Framing-Fehlern

- Synchroner Modus mit interner oder externer Zeichensynchronisation auf 1 oder 2 synchrone Zeichen und CRC-Generierung und -Prüfung mit CRC-16 oder CRC-CCITT, die entweder auf 1s oder 0s eingestellt sind

- SDLC/HDLC-Modus mit umfassender Kontrolle auf Frame-Ebene, automatischer Nulleinfügung und -löschung, Behandlung von I-Feld-Resten, Abbruchgenerierung und -erkennung, CRC-Generierung und -Prüfung sowie SDLC-Schleife

- Software-Interrupt-Bestätigungsfunktion (nicht verfügbar mit NMOS)

- Lokale Loopback- und Auto-Echo-Modi

- Unterstützt T1 Digital Trunk76

- Verbesserte DMA-Unterstützung (nicht verfügbar mit NMOS), 10 x 19-Bit-Status-FIFO und 14-Bit-Byte-Zähler

- Geschwindigkeiten:

- Z85C3O: 8,5 MHz, 10 MHz und 16,4 MHz

- Z80C3O: 8 MHz und 10 MHz

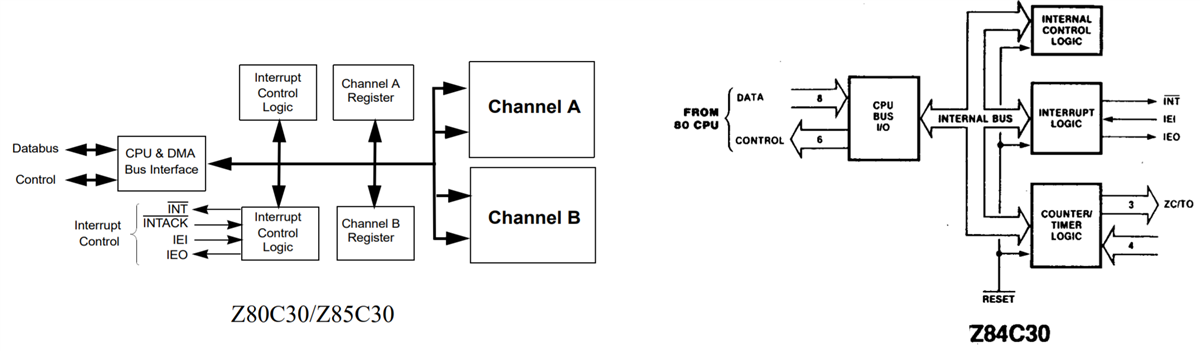

Funktionale Blockdiagramme

Veröffentlichungsdatum: 2021-11-15

| Aktualisiert: 2025-05-12