Texas Instruments TMS320VC5510A Festpunkt-DSPs

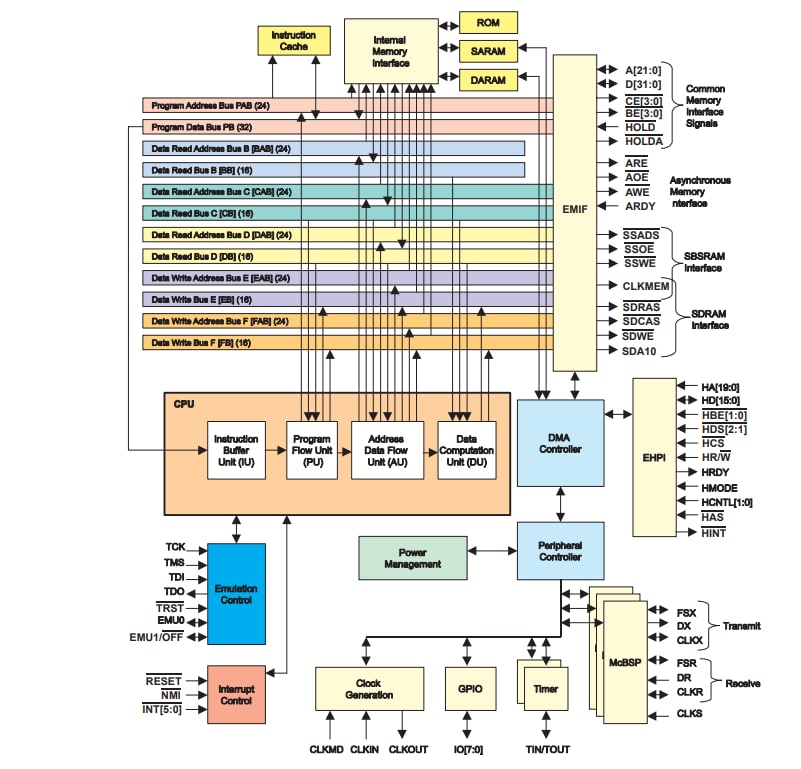

Texas Instruments TMS320VC5510A Digitale Festpunkt-Signalprozessoren basieren auf dem TMS320C55x DSP-Generierungs-CPU-Prozessorkern. Diese Bauteile verfügen über eine C55x™-DSP-Architektur, die eine hohe Leistungsfähigkeit und einen geringen Stromverbrauch durch erhöhte Parallelität und einen vollständigen Fokus auf die Reduzierung der Verlustleistung erzielt Die CPU unterstützt eine interne Busstruktur, die aus einem Programmbus, drei Lese-Datenbusse, zwei Schreib-Datenbusse und weiteren Bussen für Peripherie- und DMA-Aktivitäten besteht. Diese Busse bieten in einem einzigen Zyklus die Möglichkeit, bis zu drei Datenlesungen und zwei Datenschreibungen auszuführen. Der DMA-Controller kann bis zu zwei Datenübertragungen pro Zyklus parallel und unabhängig von der CPU-Aktivität durchführen.Die TMS320VC5510A C55x-CPU bietet zwei mehrfach akkumulierte (MAC) Einheiten, die jeweils eine 17-Bit-x-17-Bit-Multiplikation in einem einzigen Zyklus ermöglichen. Eine zentrale 40-Bit-Arithmetik- und Logikeinheit (ALU) wird durch eine zusätzliche 16-Bit-ALU unterstützt. Die Verwendung der ALUs erfolgt unter der Befehlssatzsteuerung und bietet die Möglichkeit, die parallele Aktivität und den Stromverbrauch zu optimieren. Diese Ressourcen werden in der Adresseinheit (AU) und Dateneinheit (DU) der C55x-CPU verwaltet.

Der TMS320C55x DSP-Core wurde mit einer offenen Architektur erstellt, die eine applikationsspezifische Hardware zur Steigerung der Leistungsfähigkeit auf spezifischen Algorithmen ermöglicht. Die Erweiterungen ermöglichen dem TMS320VC5510A eine außergewöhnliche Video-Codex-Leistung mit mehr als der Hälfte seiner Bandbreite, die für zusätzliche Funktionen, wie z. B. Farbraum-Umwandlung, Benutzerschnittstellen-Betriebsabläufe, Sicherheit, TCP/IP, Spracherkennung und Text-zu-Sprachen-Umwandlung verfügbar ist.

Merkmale

- TMS320C55x™ Stromsparender digitaler Festpunkt-Signalprozessor (DSP) mit hoher Leistungsfähigkeit

- Befehlszykluszeit: 6,25/5 ns

- Taktrate: 160/200 MHz

- Ein/zwei Befehle werden pro Zyklus ausgeführt

- Dual-Multiplikatoren (bis zu 400 Millionen Multiply-Accumulates pro Sekunde (MMACS))

- Zwei Rechen-/Logikeinheiten

- Ein interner Programmbus

- Drei interne Daten-/Operand-Lesebusse

- Zwei interne Daten-/Operand-Schreibbusse

- Befehlscache (24 Kbyte)

- 160 K × 16-Bit-On-Chip-RAM bestehend aus:

- Acht Blöcke von 4K × 16-Bit-Dual-Access-RAM (DARAM) (64 Kbyte)

- 32 Blöcke von 4K × 16-Bit-Single-Access-RAM (SARAM) (256 Kbyte)

- Externe 32-Bit-Speicherschnittstelle (EMIF) mit einer nahtlosen Schnittstelle zu:

- Asynchroner statischer RAM (SRAM)

- Asynchroner EPROM

- Synchroner DRAM (SDRAM)

- Synchroner Burst-SRAM (SBSRAM)

- 16 K x 16-Bit-On-Chip-ROM (32 Kbyte)

- 8 M × 16-Bit maximaler adressierbarer externer Speicherplatz

- Programmierbare stromsparende Steuerung von sechs Bauteil-Funktionsbereichen

- On-Chip-Peripherie

- Zwei 20-Bit-Timer

- Sechskanal-Direct-Memory-Access(DMA)-Controller

- Drei gepufferte serielle Mehrkanal-Anschlüsse (McBSPs)

- Verbesserte parallelgeschaltete 16-Bit-Hostanschluss-Schnittstelle (EHPI)

- Programmierbarer digitaler Phasenregelschleifen(DPLL)-Taktgeber

- Acht Universal-I/O-Pins (GPIO) und ein dedizierter Universal-Ausgang (XF)

- Scan-basierte On-Chip-Emulationslogikschaltung

- IEEE Std 1149.1 (JTAG) Boundary-Scan-Logikschaltung

- MicroStar-BGA™ mit 240 Anschlüssen; (Ball-Grid-Array) (GGW-Suffix)

- MicroStar-BGA™ mit 240 Anschlüssen; (Ball-Grid-Array) (ZGW-Suffix) [bleifrei]

- I/O-Versorgungsspannung: 3,3 V

- Core-Versorgungsspannung: 1,6 V

Applikationen

- Komprimierung

- Videoverarbeitung

- Maschinelle Bildverarbeitung

- Medizinische Bildverarbeitung

Weitere Ressourcen

Blockdiagramm