Texas Instruments TMS320VC5507 Digitaler Festpunkt-Signalprozessor

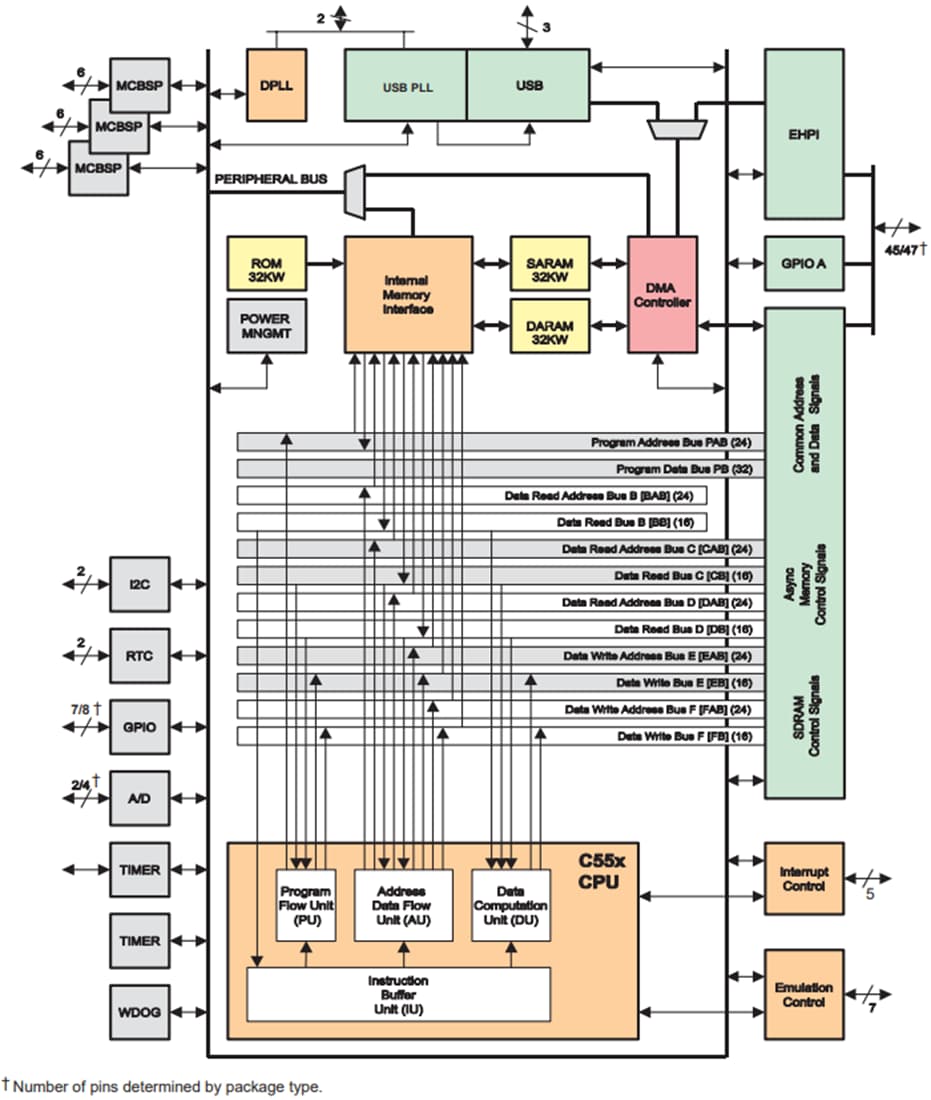

Der Texas Instruments TMS320VC5507 digitale Festpunkt-Signalprozessor (DSP) basiert auf dem TMS320C55x DSP-Generierungs-CPU-Prozessorkern. Die DSP-Architektur von Texas Instruments TMS320C55x erreicht hohe Leistung und geringen Stromverbrauch durch erhöhte Parallelität und den Fokus auf die Reduzierung der Verlustleistung. Die CPU unterstützt eine interne Busstruktur, die aus einem Programmbus, drei Lese-Datenbusse, zwei Schreib-Datenbusse und weiteren Bussen für Peripherie- und DMA-Aktivitäten besteht. Diese Busse bieten in einem einzigen Zyklus die Möglichkeit bis zu drei Datenlesungen und zwei Datenschreibungen auszuführen. Parallel dazu kann der DMA-Controller bis zu zwei Datenübertragungen pro Zyklus durchführen, unabhängig von der CPU-Aktivität.Die TMS320C55x CPU bietet zwei mehrfach akkumulierte (MAC) Einheiten, die jeweils eine 17-Bit- x 17-Bit-Multiplikation in einem einzigen Zyklus ermöglichen. Eine zentrale 40-Bit-Arithmetik- und Logikeinheit (ALU) wird durch eine zusätzliche 16-Bit-ALU unterstützt. Die Verwendung der ALUs erfolgt unter der Befehlssatzsteuerung und bietet die Möglichkeit, die parallele Aktivität und den Stromverbrauch zu optimieren. Diese Ressourcen werden in der Adresseinheit (AU) und Dateneinheit (DU) der TMS320C55x CPU verwaltet. Die TMS320C55x DSP-Generierung unterstützt einen variablen Bytebreiten-Befehlssatz für eine verbesserte Codedichte. Die Befehlseinheit (IU) führt 32-Bit-Programmabrufe aus internen oder externen Speicher- und Warteschlangenbefehle für die Programmeinheit (PU) durch. Die Programmeinheit dekodiert die Befehle, leitet Aufgaben an die AU- und DU-Ressourcen weiter und verwaltet die vollständig geschützte Pipeline. Die Sprungvorhersagefunktion vermeidet Pipeline-Flushes bei der Ausführung von bedingten Befehlen.

Der 128-Kbyte-On-Chip-Speicher auf dem TMS320VC5507 ist ausreichend für viele Handheld-Geräte, tragbare GPS-Systeme, drahtlose Freisprechtelefone, tragbare PDAs und Spielekonsolen. Viele dieser Applikationen benötigen in der Regel einen 64-KByte- oder größeren, aber weniger als 128-KByte-On-Chip-Speicher und müssen mehr als 60 % bis 70 % der Zeit im Standby-Modus betrieben werden. Für Applikationen, die mehr als 128 KByte On-Chip-Speicher aber weniger als 256 KByte On-Chip-Speicher erfordern, bietet Texas Instruments den TMS320VC5509A, der auf dem TMS320C55x DSP-Core basiert. Die Universal-Eingangs- und Ausgangsfunktionen zusammen mit dem 10-Bit-Analog-Digital-Wandler bieten ausreichend Pins für Status, Interrupts und Bit-I/O für LCD-, Tastatur- und Medienschnittstellen. Die parallelgeschaltete Schnittstelle arbeitet in zwei Modi, entweder als Slave zu einem Mikrocontroller, der den HPI-Anschluss verwendet oder als parallelgeschaltete Medienschnittstelle mit dem asynchronen EMIF. Serielle Medien werden über drei McBSPs unterstützt.

Der TMS320C5507 Peripheriesatz enthält eine externe Speicherschnittstelle (EMIF), die einen nahtlosen Zugriff auf asynchrone Speicher, wie z. B. EPROM und SRAM sowie auf Hochgeschwindigkeits-Speicher mit hoher Dichte, wie z. B. synchroner DRAM bietet. Weitere Peripheriegeräte sind ein Universal Serial Bus (USB), eine Echtzeituhr, ein Watchdog-Timer und eine I2C Multi-Master- und Slave-Schnittstelle. Drei gepufferte serielle Vollduplex-Mehrkanal-Anschlüsse (McBSPs) bieten eine nahtlose Schnittstelle zu einer großen Auswahl von seriellen Industriestandard-Bauteilen und eine Mehrkanal-Kommunikation mit bis zu 128 separat aktivierten Kanälen. Die erweiterte Hostanschluss-Schnittstelle (HPI) ist eine parallelgeschaltere 16-Bit-Schnittstelle, die der Hostprozessor-Schnittstelle Zugang zu einem internen 32-KByte-Speicher auf dem TMS320C5507 ermöglicht. Der HPI kann entweder im Multiplex- oder nicht-Multiplex-Modus konfiguriert werden, um eine nahtlose Schnittstelle zu einer großen Auswahl von Hostprozessoren zu bieten. Der DMA-Controller bietet eine Datenverschiebung für sechs unabhängige Kanalkontexte ohne CPU-Eingriff, wodurch ein DMA-Durchsatz von bis zu zwei 16-Bit-Wörter pro Zyklus ermöglicht wird. Zwei Universal-Timer, bis zu acht dedizierte Universal-I/O-Pins (GPIO) und eine digitale Phasenregelschleifen(DPLL)-Taktgenerierung sind ebenfalls enthalten.

Merkmale

- TMS320C55™ Stromsparender digitaler Festpunkt-Signalprozessor mit hoher Leistungsfähigkeit

- Befehlszykluszeit: 9,26 ns, 6,95 ns, 5 ns

- Taktrate: 108, 144, 200 MHz

- Ausführung von einem/zwei Befehl(en) pro Zyklus

- Dual-Multiplikatoren [bis zu 200 Millionen Multiply-Accumulates pro Sekunde (MMACS)]

- Zwei Arithmetic/Logic Units (ALUs)

- Drei interne Daten-/Operand-Lesebusse und zwei interne Daten-/Operand-Schreibbusse

- 64K × 16-Bit-On-Chip-RAM bestehend aus

- 64 Kbyte Dual-Access-RAM (DARAM), 8 Blöcke 4K × 16-Bit

- 64 Kbyte Single-Access-RAM (SARAM), 32 Blöcke 4K × 16-Bit

- 64 Kbyte One-Wait-State-on-Chip-ROM (32K × 16-Bit)

- 8M × 16-Bit maximaler adressierbarer externer Speicherplatz (synchroner DRAM)

- Externer parallelgeschalteter 16-Bit-Bus-Speicher, der Folgendes unterstützt:

- Externe Speicherschnittstelle (EMIF) mit GPIO-Funktionen und nahtloser Schnittstelle zu

- Asynchroner statischer RAM (SRAM)

- Asynchrone EPROM

- Synchroner DRAM (SDRAM)

- Verbesserte parallelgeschaltete 16-Bit-Hostanschluss-Schnittstelle (EHPI) mit GPIO-Funktionen

- Externe Speicherschnittstelle (EMIF) mit GPIO-Funktionen und nahtloser Schnittstelle zu

- Programmierbare stromsparende Steuerung von sechs Bauteil-Funktionsbereichen

- Scan-basierte On-Chip-Emulationslogikschaltung

- On-Chip-Peripherie

- Zwei 20-Bit-Timer

- Watchdog-Timer

- Sechskanal-DMAC (Direct-Memory-Access-Controller)

- Drei gepufferte serielle Mehrkanal-Anschlüsse (McBSPs)

- Programmierbarer Phasenregelschleifen(PLL)-Taktgeber

- Sieben (LQFP) oder acht (BGA) Universal-I/O-Pins (GPIO) und einen Universal-Ausgangs-Pin (XF)

- USB-Full-Speed-Slave-Anschluss (12 Mbps), der Bulk-, Interrupt- und isochrone Übertragungen unterstützt

- Inter-Integrated Circuit (I2C) Multi-Master- und Slave-Schnittstelle

- Echtzeituhr (RTC) mit Quarzeingang, separatem Taktbereich und separater Stromversorgung

- 4-Kanal(BGA)- oder 2-Kanal(LQFP)-10-Bit-Analog-Digital-Wandler mit sukzessiver Approximation

- IEEE Std 1149.1 (JTAG) Boundary-Scan-Logik

- Gehäuse

- 144-Pin-Quad-Flatpack mit niedrigem Profil (LQFP) (PGE-Suffix)

- 179-Pin-MicroStar-BGA™ (Ball Grid Array) (GHH- und ZHH-Suffixe)

- 1,2-V-Core (108 MHz), 2,7 V bis 3,6 V I/Os

- 1,35-V-Core (144 MHz), 2,7 V bis 3,6 V I/Os

- 1,6-V-Core (200 MHz), 2,7 V bis 3,6 V I/Os

Funktionales Blockdiagramm