Texas Instruments TMS320F28P65x/TMS320F28P65x-Q1 Echtzeit-MCUs

Die Echtzeit-Mikrocontroller (MCUs) TMS320F28P65x/TMS320F28P65x-Q1 von Texas Instruments gehören zur C2000™ -Echtzeit-Mikrocontroller-Familie skalierbarer Bauteile mit extrem niedriger Latenz. Die C2000-MCUs wurden für Effizienz in der Leistungselektronik entwickelt, u. a. für hohe Leistungsdichte und Schaltfrequenzen. Außerdem unterstützen die Bauteile die Verwendung von IGBT-, GaN- und SiC-Technologien.Das Echtzeitsteuerungssubsystem des Mikrocontrollers TMS320F28P65x/TMS320F28P65x-Q1 von TI basiert auf dem 32-Bit-C28x-DSP-Kern, der in jedem Kern eine Signalverarbeitungsleistung von 200 MIPS für Fließkomma- oder Festkomma-Code bietet, der entweder vom On-Chip-Flash oder SRAM ausgeführt werden. Die Bauteile der Serie TMS320F28P65x-Q1 sind nach AEC-Q100 für Anwendungen in der Automobilindustrie qualifiziert.

Merkmale

- Echtzeitverarbeitung

- Enthält bis zu drei CPUs: zwei C28x 32-Bit-DSP-CPUs und eine CLA-CPU, die alle mit 200 MHz betrieben werden

- Bietet eine Gesamtverarbeitungsleistung, die der eines Arm® Cortex®-M7-basierten Geräts mit 1000 MHz entspricht, bei Echtzeit-Signalkettenleistung

- C28x DSP-Architektur

- IEEE 754 Doppel-Präzisions-Fließkommaeinheit (64-Bit)

- Trigonometric Math Unit (TMU)

- Schnelle ganzzahlige Division (FINTDIV)

- CRC-Motor und Anweisungen (VCRC)

- Control Law Accelerator (CLA) CPU

- IEEE 754 Einfachpräzisions-Gleitkomma

- Führt unabhängig von C28x-CPUs Code aus

- Analoges Subsystem

- Drei Analog-Digital-Wandler (ADCs)

- 16-Bit-Modus, jeweils 1,19 MSPS

- 12-Bit-Modus, jeweils 3,92 MSPS

- Bis zu 40 einendige oder 19 differentielle Eingänge

- Getrennte Abtast- und Haltefunktion (S/H) an jedem ADC, um gleichzeitige Messungen zu ermöglichen

- Hardware-Nachbearbeitung von Umwandlungen

- Hardware-Überabtastungs- (bis zu 128x) und Unterabtastmodi mit Akkumulation, Mittelwertbildung und Ausreißer-Unterdrückung

- 24 redundante Eingangskanäle für Flexibilität

- Automatischer Vergleich der Umwandlungsergebnisse für funktionale Sicherheitsapplikationen

- 11 Komparatoren mit Fenster und 12-Bit-Digital-Analog-Wandler-Referenzen (DAC)

- DAC mit Neigungsausgleich — ermöglicht Spitzenstrom- und Talstrommodussteuerung

- Verbindungsoptionen für internen Temperatursensor und ADC-Referenz

- Zwei gepufferte 12-Bit-DAC-Ausgänge

- Zwei CAN-FD-/MCAN-Controller-Area-Netzwerke mit flexibler Datenrate

- Drei Analog-Digital-Wandler (ADCs)

- System-Peripherie

- Zwei 6-Kanal-DMA-Controller (Direct Memory Access, DMA)

- 185 individuell programmierbare Multiplex-Universal-Ein-/Ausgangs-Pins (GPIO)

- Erweiterter Peripheral Interrupt controller (ePIE)

- Unterstützung für Stromsparmodus (LPM)

- Embedded-Echtzeit-Analyse und -Diagnose (ERAD)

- Hintergrund-CRC (BGCRC)

- Sicherheitsperipherie

- Advanced Encryption Standard (AES-128, 192, 256) Beschleuniger

- Sicherheit

- JTAGLOCK

- Zero-Pin-Boot

- Dual-Zonen-Sicherheit

- Eindeutige Identifizierungsnummer (UID)

- Sicherheitsperipherie

- Einfachere Umsetzung durch Gegenüberstellung

- Lockstep auf C28x CPU 2

- Speicher-Einschalt-Selbsttest (MPOST)

- Hardware-integrierter Selbsttest (HWBIST)

- Für die funktionale Sicherheit ausgelegt

- Für funktionale Sicherheitsapplikationen ausgelegt

- Dokumentation zur Unterstützung des Systemdesigns gemäß ISO 26262 und IEC 61508 wird verfügbar sein

- Systematische Fähigkeit bis zu ASIL D und SIL 3 ausgerichtet

- Hardware-Fähigkeit bis zu ASIL B und SIL 2 ausgerichtet

- Sicherheitsbezogene Zertifizierung

- ISO 26262 und IEC 61508 Zertifizierung bis zu ASIL B und SIL 2 durch TÜV SÜD geplant

- Takt- und Systemsteuerung

- Zwei interne 10-MHz-Oszillatoren

- On-Chip-Quarzoszillator

- 2 * APLL, BOR, redundanter interrupt-Vektor-RAM

- Watchdog-Timer-Modul mit Fenster

- Fehlende Takterkennungsschaltung

- Dual-Takt-Komparator (DCC)

- Live-Firmware-Update (LFU)

- Schneller Kontextwechsel von alter zu neuer FirmWare mit oder ohne Leistungszyklus

- 1,2 V Core, 3,3 V I/O-Design

- Interner VREG für 1,2 V Generierung

- Spannungsabfall-Reset-Schaltung (BOR)

- Speicher

- 1,28 MB CPU-mappable Flash (ECC-geschützt) mit fünf Flash-Bänken

- 248 KB RAM (verbesserte Paritätsschutz)

- Externe Speicherschnittstelle (EMIF) mit ASRAM, SDRAM-Unterstützung oder ASIC/FPGA

- Steuerungsperipherie

- 36 Pulsweitenmodulatorkanäle (PWM), alle mit 150 ps hoher Auflösung (HRPWM)

- Unterstützung für Mindest-Totband-Logikschaltung (MINDB), illegale Combo-Logikschaltung (ICL) und andere Sonderfunktionen (d. h. Dioden-Emulation [DE])

- Ermöglicht die Unterstützung von Matrixwandlern, Multilevel-Wandlern und Resonanzwandlern ohne zusätzliche externe Logik

- Sieben eCAP-Module (Enhanced Capture, eCAP)

- High-Resolution Capture (HRCAP) ist auf zwei der sieben eCAP-Module verfügbar

- Zwei neue Überwachungseinheiten für Flanke, Impulsbreite und Periode, die mit ePWM Stroboskopen und Auslöseereignissen gekoppelt werden können

- Mehr 256 Eingänge für mehr Erfassungsoptionen

- Neue ADC SOC-Generierungsfähigkeit

- eCAP kann auch für zusätzliche PWM verwendet werden

- Sechs eQEP-Module (Enhanced Quadrature Encoder Pulse, eQEP)

- 16 Sigma-Delta-Filtermodul-Eingangskanäle (SDFM), zwei unabhängige Filter pro Kanal

- Embedded-Mustergenerator (EPG)

- Konfigurierbarer Logikblock

- Sechs Logik-Kacheln zur Erweiterung der bestehenden Peripherieleistung oder Definition einer benutzerdefinierten Logik zur Reduzierung oder Entfernung von externem CPLD/FPGA

- Unterstützt Encoder-Schnittstellen ohne die Notwendigkeit von FPGA

- Ermöglicht eine benutzerdefinierte PWM-Generierung für die Leistungsumwandlung

- 36 Pulsweitenmodulatorkanäle (PWM), alle mit 150 ps hoher Auflösung (HRPWM)

- Kommunikationsperipherie

- EtherCAT® SubordinateDevice (oder SubDevice) Controller (ESC)

- USB 2.0 (MAC + PHY)

- Schnelle Serielle Schnittstelle (FSI) ermöglicht einen Datenaustausch von bis zu 200 MBit/s über die Isolierung

- Vier Hochgeschwindigkeits-SPI-Anschlüsse (bis zu 50MHz)

- Vier serielle Kommunikationsschnittstellen (SCI) (Unterstützung für UART)

- Zwei asynchrone Hochgeschwindigkeits- (25Mbps) -Universal-Empfänger/-Sender (UARTs)

- ZweiI2C-Schnittstellen(400 kBit/s)

- Externe Boot-Option über SPI/SCI/I2C

- Zwei UART-kompatible LIN-Module (Local Interconnect Network, LIN) (unterstützt SCI)

- Leistungsmanagement-Bus-Schnittstelle (PMBus) (unterstütztI2C)

- Ein Controller Area Netzwerk (CAN/DCAN)

- Gehäuseoptionen:

- Bleifreies, umweltfreundliches Gehäuse

- Neues Fine Pitch Ball Grid Array (nFBGA) mit 256 Kugeln [Suffix ZEJ], 13 mm × 13 mm / 0,8 mm Raster

- 176-poliges PowerPAD™ thermisch verbessertes Low-Profile-Quad-Flatpack (HLQFP) [Suffix PTP], 26 mm × 26 mm / 0,5 mm Raster

- Neues Fine Pitch Ball Grid Array (nFBGA) mit 169 Kugeln [NMR-Suffix], 9mm × 9mm/0,65mm Raster

- 100-poliges PowerPAD™ Thermisch verbessert, dünn

- Quad Flatpack (HTQFP) [PZP-Suffix], 16 mm × 16 mm/0,5 mm Rastermaß

- Umgebungstemperatur (TA): -40 °C bis 125 °C (für Industrieapplikationen und Fahrzeuganwendungen geeignet)

Applikationen

- Servoantrieb-Steuermodul

- Roboter-Servoantrieb

- CNC-Steuerung

- Mobile Roboter-Motorsteuerung

- Große kommerzielle HLK-Motorsteuerung

- Linearer Motorsegment-controller

- Zentraler Wechselrichter

- String-Wechselrichter

- Leistungsumwandlungssystem

- DC-Schnellladestation

- Wechselrichter und Motorsteuerung

- Industrie-AC/DC

- Dreiphasige USV

- Einphasige Online-USV

- Händlernetzwerk und Server-Netzteil

- On-Board- (OBC) und drahtloses Ladegerät

- Kompressormodul für HLK-Anlagen

- Scheinwerfer

Datenblätter

Videos

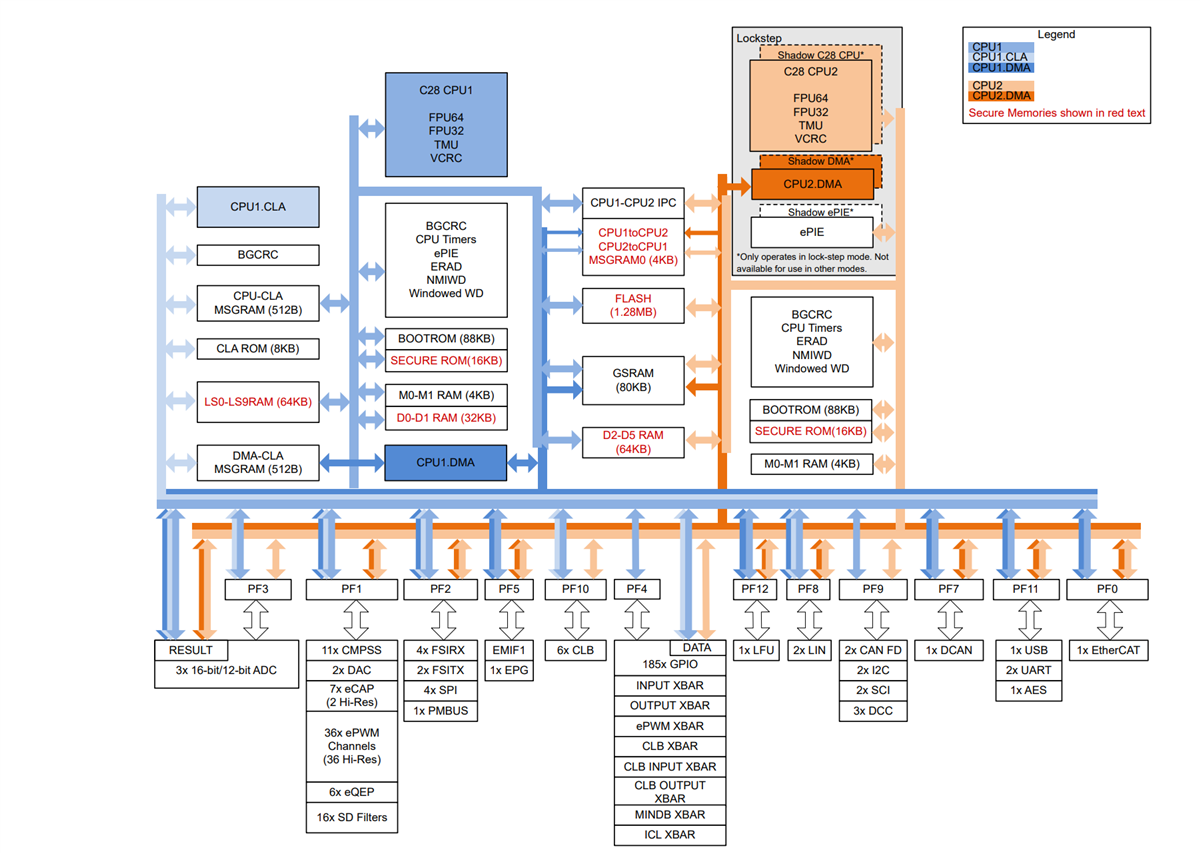

Funktionales Blockdiagramm

Weitere Ressourcen

Veröffentlichungsdatum: 2023-12-28

| Aktualisiert: 2025-05-08