Texas Instruments CDCU877 Phasenregelschleifen-Takttreiber

Der Texas Instruments CDCU877 Phasenverriegelungs-Loop-Takttreiber ist ein leistungsstarker Buffer mit geringem Jitter, geringem Versatz und Null-Verzögerung. Das Bauteil verteilt ein Differential-Takteingangspaar (CK, /CK) auf 10 differentielle Paare von Taktausgängen (Yn, /Yn) und ein differentielles Paar von Rückkopplungs-Taktausgängen (FBOUT, /FBOUT). Die Taktausgänge werden durch die Eingangstaktgeber (CK, /CK), die Rückkopplungstaktgeber (FBIN, /FBIN), die LVCMOS-Steuerpins (OE, OS) und den analogen Stromeingang (AVDD) gesteuert. Wenn OE niedrig ist, sind die Taktausgänge, außer FBOUT, /FBOUT deaktiviert, während die interne PLL seine verriegelte Frequenz aufrechterhält. OS (Output Select) ist ein Programmpin, der an GND oder VDD angeschlossen werden muss. Wenn OS hoch ist, funktioniert OE wie zuvor beschrieben. Wenn OS und OE beide niedrig sind, wirkt sich OE nicht auf Y7, /Y7 aus, da diese freilaufend sind. Wenn AVDD geerdet ist, ist die PLL ausgeschaltet und wird zu Testzwecken überbrückt.Wenn sich beide Takteingänge (CK, /CK) auf einem niedrigen Logikpegel befinden, wechselt das Bauteil in einen Stromsparmodus. Eine Schaltung zur Erkennung der Eingangslogikschaltung an den Differentialeingängen, die von den Eingangsbuffern unabhängig ist, erkennt die Logikschaltung bei einem niedrigen Pegel und arbeitet in einem stromsparenden Zustand, in dem alle Ausgänge, die Rückkopplung und die PLL ausgeschaltet sind. Wenn die Takteingänge von der niedrigen Logikschaltung zu Differential-Signalen wechseln, schaltet sich die PLL wieder ein. Die Eingänge und Ausgänge werden dann aktiviert und die PLL erreicht innerhalb der festgelegten Stabilisierungszeit eine Phasenverriegelung zwischen dem Rückkopplungstaktpaar (FBIN, /FBIN) und dem Takteingangspaar (CK, /CK). Der CDCU877 von Texas Instruments kann eine Frequenzspreizungstaktung (SSC) nachverfolgen, um EMI zu reduzieren. Dieses Bauteil wird von 0 °C bis +70 °C betrieben.

Merkmale

- 1,8-V-Phasenregelschleifen-Takttreiber für Doppeldatenraten-Applikationen (DDR II)

- Frequenzspreizungstakt-kompatibel

- Betriebsfrequenz: 10 MHz bis 400 MHz

- Niedriger Stromverbrauch: < 135 mA

- Geringer Jitter: ±30 ps (Zyklus-zu-Zyklus)

- Niedriger Ausgangsversatz: 35 ps

- Geringer Periodenjitter: ±20 ps

- Niedriges dynamisches Phasen-Offset: ±15 ps

- Niedriges statisches Phasen-Offset: ±50 ps

- Verteilt einen Differential-Takteingang auf 10 Differential-Ausgänge

- 52-Ball-µBGA (MicroStar™ Junior-BGA, 0,65 mm Rastermaß) und 40-Pin-MLF

- Externe Feedback-Pins (FBIN, FBIN) werden zur Synchronisierung der Ausgänge mit den Eingangstakten verwendet

- Erfüllt oder übertrifft den JESD82-8 PLL-Standard für PC2-3200/4300

- Ausfallsichere Empfängereingänge

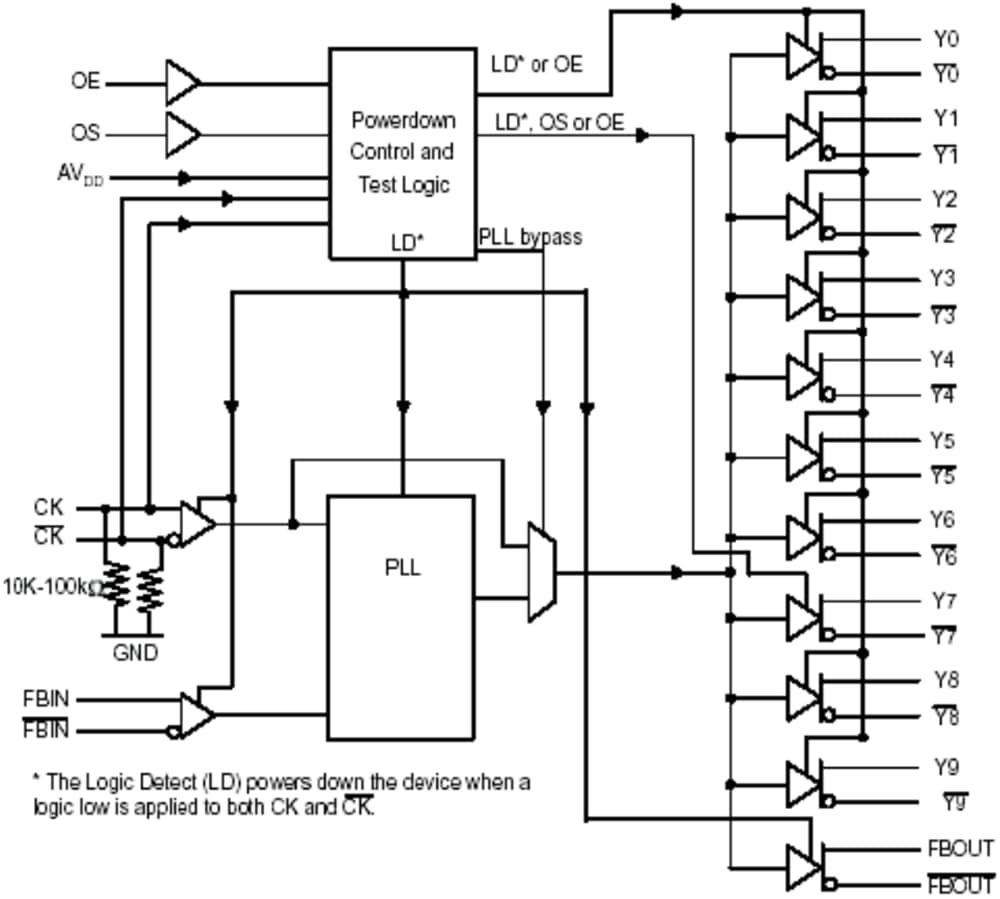

Logik-Diagramm