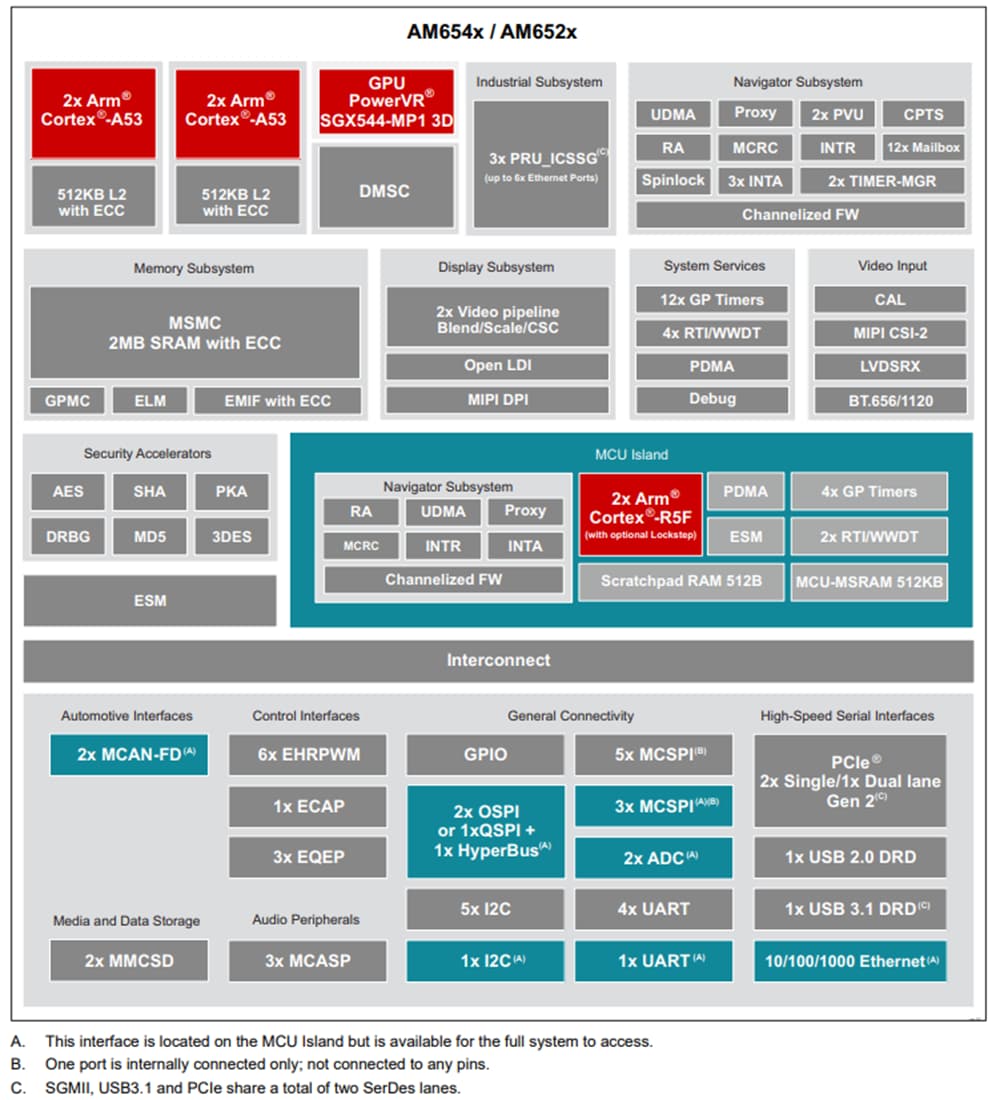

Texas Instruments AM654x/AM652x ARM™-basierte Prozessoren

Die Arm™-basierten Prozessoren AM654x/AM652x von Texas Instruments sind Arm® Applikationsprozessoren, die für die komplexen Verarbeitungsanforderungen moderner Industrie 4.0 Embedded-Produkte entwickelt wurden. Die Geräte AM654x und AM652x kombinieren vier oder zwei ARM® Cortex®-A53 Kerne mit einem Dual-Arm-Cortex-R5F-MCU-Subsystem. Dazu gehören Funktionen, die Kunden dabei helfen sollen, funktionale Sicherheitsziele für Endprodukte zu erreichen. Es enthält außerdem drei Gigabit-Subsysteme für die industrielle Kommunikation (PRU_ICSSG), um ein SoC zu schaffen, das leistungsstarke industrielle Steuerungen mit industrieller Konnektivität und Verarbeitung für funktionale Sicherheitsanwendungen ermöglicht. AM65xx wird zur Zeit von TÜV SÜD nach IEC 61.508zertifiziert.Die vier ARM-Cortex-A53-Kerne im AM654x sind in zwei Dual-Core-Clustern mit gemeinsamem L2-Speicher angeordnet, um zwei Verarbeitungskanäle zu schaffen. Die beiden ARM Cortex-A53-Cores im AM652x sind in einem einzelnen Dual-Core-Cluster und zwei Single-Core-Cluster-Optionen erhältlich. Ein umfangreiches ECC ist auf einem On-Chip-Speicher, einer Peripherie und einer Verbindung für Zuverlässigkeit enthalten. Der SoC als Ganzes verfügt über Funktionen, die den Kunden bei der Entwicklung von Systemen helfen sollen, die die Ziele der funktionalen Sicherheit erreichen können. Kryptografische Beschleunigung und sicheres Booten sind auf einigen AM654x- und AM652x-Bauteilen zusätzlich zu granularen Firewalls, die vom DMSC verwaltet werden, verfügbar.

Die ARM Cortex-A53-RISC-CPUs bieten eine Programmierbarkeit mit ARM™ Neon-Erweiterung. Das ARM Cortex-R5F Dual-MCU-Subsystem ist für den allgemeinen Einsatz als zwei Cores verfügbar oder kann in Lockstep verwendet werden, um die Anforderungen von funktionalen Sicherheitsapplikationen zu erfüllen. Die PRU_ICSSG-Subsysteme können verwendet werden, um bis zu sechs Ports für industrielles Ethernet wie Profinet IRT, TSN, Ethernet/IP oder EtherCAT (neben vielen anderen) bereitzustellen, oder sie können für Standard-Gigabit-Ethernet-Konnektivität verwendet werden.

Texas Instruments bietet einen kompletten Satz von Software und Entwicklungstools für die ARM Cores, einschließlich Prozessor SDK Linux, Linux-RT, RTOS, Android, C-Compiler und eine Debugging-Schnittstelle für die Transparenz bei der Ausführung von Quellcode. Zur Unterstützung der Kunden bei der Entwicklung von funktionalen Sicherheits- oder sicherheitsbezogenen Systemen werden anwendbare funktionale Sicherheits-und Sicherheitsdokumentation zur Verfügung gestellt.

Merkmale

- Prozessorkerne

- ARM Cortex-A53-Dual- oder Quad-Core-Mikroprozessor- Subsystem bei bis zu 1,1 GHz

- Bis zu zwei Dual-Core- oder zwei Single-Core-ARM-Cortex-A53-Cluster mit 512 KB L2-Cache einschließlich SECDED

- Jeder A53-Core verfügt über 32 KB L1 ICache und 32 K L1 DCache

- Dual-Core-ARM-Cortex-R5F bei bis zu 400 MHz

- Unterstützt Lockstep-Modus

- 16 KB ICache, 16 KB DCache und 64 KB RAM pro R5F-Core

- ARM Cortex-A53-Dual- oder Quad-Core-Mikroprozessor- Subsystem bei bis zu 1,1 GHz

- Industrie-Subsystem

- Drei industrielle Gigabit-Kommunikations-Subsysteme (PRU_ICSSG)

- Bis zu zwei 10/100/1000 Ethernet-Anschlüsse pro PRU_ICSSG

- Unterstützt zwei SGMII-Anschlüsse

- Kompatibilität mit 10/100 Mb PRU-ICSS

- 24× PWMs pro PRU_ICSSG

- Zyklus-für-Zyklus-Steuerung

- Verbesserte Auslösesteuerung

- 18× Sigma-Delta-Filter pro PRU_ICSSG

- Kurzschluss-Logikschaltung

- Überstrom-Logikschaltung

- 6× Multiprotokoll-Positions-Encoder-Schnittstellen gemäß PRU_ICSSG

- Drei industrielle Gigabit-Kommunikations-Subsysteme (PRU_ICSSG)

- Speicher-Subsystem

- Bis zu 2 MB On-Chip-L3-RAM mit SECDED

- Multicore-Shared-Memory-Controller (MSMC)

- Bis zu 2 MB (2 Bänke × 1 MB) SRAM mit SECDED

- Gemeinsam genutzter, kohärenter SRAM-Speicher der Stufe 2 oder Stufe 3

- Gemeinsamer, kohärenter Level-3-Cache

- 256-Bit-Prozessoranschlussbus und 40-Bit-Bus für physikalische Adressen

- Kohärente, einheitliche bidirektionale Schnittstellen zur Verbindung mit Prozessoren oder Bauteil-Master

- L2-, L3-Cache-Vorwärmung und Nachspülung

- Bandbreitenmanagement mit Starvation Boundation

- Eine Infrastruktur-Master-Schnittstelle

- Einzelne externe Speicher-Master-Schnittstelle

- Unterstützt ein verteiltes virtuelles System

- Unterstützt interne DMA-Engine – Data Routing Unit (DRU) (DRU)

- ECC-Fehlerschutz

- Bis zu 2 MB (2 Bänke × 1 MB) SRAM mit SECDED

- DDR-Subsystem (DDRSS)

- Unterstützt DDR4-Speichertypen bis zu DDR-1600

- 32-Bit-Datenbus und 7-Bit-SECDED-Bus

- 8 GB adressierbarer Gesamtplatz

- Universal-Speicher-Controller (GPMC)

- SafeTI™ Halbleiter-Komponente

- Konzipiert für Applikationen der funktionalen Sicherheit

- Entwickelt gemäß den Anforderungen von IEC 61508

- Erreicht die systematische Integrität von SIL-3

- Für die MCU-Sicherheitsinsel sind ausreichende Diagnosen vorgesehen, um die Anforderungen an die zufällige Fehlerintegrität von SIL-2 zu erfüllen.

- Für den Rest des SoCs sind ausreichende Diagnosefunktionen enthalten, um die Anforderungen an die zufällige Fehlerintegrität von SIL-2 zu erfüllen.

- Darüber hinaus sind ausreichende architektonische Metriken vorhanden, um die Ausführung von SIL-3 Anwendungen mit einem angemessenen Sicherheitskonzept zu ermöglichen (z.B. gegenseitiger Vergleich durch Software).

- Funktionssicherheits-Handbuch (FSM) verfügbar

- Sicherheitsbezogene Zertifizierung

- Zertifizierung der Funktionssicherheit auf Komponentenebene durch TÜV-SÜD [Zertifizierung in Bearbeitung]

- funktionale Sicherheitsfunktionen

- ECC oder Parität auf rechenkritischen Speichern und interner Busanbindung

- Firewalls zur Bereitstellung von Störungsfreiheit (FFI)

- Eingebauter Selbsttest (BIST) für CPU, High-End-Timer und On-Chip-RAM

- Unterstützung der Hardware-Fehlerinjektion für Test-für-Diagnose

- Fehlersignalisierungsmodule (ESM) zur Erfassung von funktionalen sicherheitsrelevanten Fehlern

- Spannungs-, Temperatur- und Taktüberwachung

- Watchdog-Timer mit Fenster und ohne Fenster in mehreren Taktdomänen

- MCU-Insel

- Isolierung des ARM Cortex-R5F Dual-Core-Mikroprozessor-Subsystems

- Separate Spannung, Takte, Rücksetzungen und dedizierte Peripherie

- Interne MCSPI-Verbindung zum Rest des SoCs

- Sicherheit

- Unterstützung für Secure Boot

- Hardware-verstärkte Root-of-Trust

- Unterstützung zum Umschalten von Root-of-Trust über einen Backup-Schlüssel

- Unterstützung für den Takeover-, IP- und Anti-Rollback-Schutz

- Kryptografische Beschleunigungsunterstützung

- Session-bewusste kryptografische Engine mit der Möglichkeit, Schlüsselmaterial basierend auf dem eingehenden Datenstrom automatisch zu schalten

- Unterstützt kryptografische Cores

- AES – 128/192/256-Bit-Schlüsselgrößen

- 3DES – 56/112/168-Bit-Schlüsselgrößen

- MD5, SHA1

- SHA2 – 224/256/384/512

- DRBG mit einem echten Zufallszahlengenerator

- PKA (public key accelerator) zur Unterstützung der RSA/ECC-Verarbeitung

- DMA-Unterstützung

- Sicherheit debuggen

- Sicherer Software-gesteuerter Debug-Zugang

- Sicherheitsbewusstes Debugging

- Unterstützung für Trusted Execution Environment (TEE)

- Arm TrustZone-basierte TEE

- Umfangreiche Firewall-Unterstützung für Isolierung

- Sicherer DMA-Pfad und sichere Verbindung

- Sicherer Watchdog/Timer/IPC

- Unterstützung für sichere Speicherung

- On-the-fly-Verschlüsselung und Authentifizierungsunterstützung für die OSPI-Schnittstelle

- Netzwerk-Sicherheitsunterstützung für Datenverschlüsselung/-authentifizierung (Nutzdaten) über eine paketbasierte kryptografische Hardware-Engine

- Sicherheits-Coprozessor (DMSC) für die Schlüssel- und Sicherheitsverwaltung, mit dedizierter Geräteebene, Verbindung für Sicherheitssoftware

- Unterstützung für Secure Boot

- SoC-Dienste

- Gerätemanagement-Sicherheitscontroller (DMSC)

- Zentralisierter SoC-Systemcontroller

- Verwaltet die Systemdienste, einschließlich des ersten Starts, der Sicherheit, der funktionalen Sicherheit und der Verwaltung von Uhr/Reset/Stromversorgung

- Energiemanagement-Controller für aktive und stromsparende Modi

- Kommunikation mit verschiedenen Verarbeitungseinheiten über Message-Manager

- Vereinfachte Schnittstelle zur Optimierung von nicht verwendeten Peripheriegeräten

- Tracing- und Debugging-Funktion

- Sechzehn 32-Bit-Universal-Timer

- Zwei Datenbewegungs- und Steuernavigator-Subsysteme (NAVSS)

- Ringbeschleuniger (RA)

- Einheitliches DMA (UDMA)

- Bis zu 2 Timer-Manager (TM) (jeweils 1024 Timer)

- Gerätemanagement-Sicherheitscontroller (DMSC)

- Multimedia

- Display-Subsystem

- Zwei vollständig zugeordnete Overlay-Manager, die mit zwei Display-Ausgängen verbunden sind

- Parallele MIPI-DPI-Schnittstelle mit einem Anschluss

- OLDI mit einem Anschluss

- PowerVR SGX544-MP1 3D-Grafik-Verarbeitungseinheit (GPU)

- Eine serielle Kamera-Schnittstelle (MIPI® CSI-2)

- Videoaufnahme mit einem Anschluss: BT.656/1120 (keine integrierte Synchronisierung)

- Display-Subsystem

- Hochgeschwindigkeits-Schnittstellen

- Eine Gigabit-Ethernet-Schnittstelle (CPSW) unterstützt

- RMII (10/100) oder RGMII (10/100/1000)

- IEEE1588 (2008 Anhang D, Anhang E, Anhang F) mit 802.1AS PTP

- Audio-/Video-Überbrückung (P802.1Qav/D6.0)

- Energy Efficient Ethernet (802.3az)

- Jumbo-Frames (2024 Byte)

- § 45 MDIO-PHY-Management

- Zwei PCI-Express (PCIe) Revision 3.1 Subsysteme

- Unterstützt den Betrieb von Gen2 (5,0 GT/s)

- Zwei unabhängige 1-spurige oder ein einzelner 2-spuriger Anschluss

- Unterstützung für gleichzeitigen Root-Komplex- und Endpunktbetrieb

- USB 3.1 Dual-Role-Device(DRD)-Subsystem

- Ein erweiterter SuperSpeed Gen1-Anschluss

- Eine USB 2.0-Anschluss

- Jeder Anschluss ist unabhängig als USB-Host, USB-Peripherie oder USB-DRD konfigurierbar

- Eine Gigabit-Ethernet-Schnittstelle (CPSW) unterstützt

- Allgemeine Konnektivität

- 6× Inter-Integrated Circuit (I2C™) Anschlüsse

- 5× konfigurierbare UART/IrDA/CIR-Module

- Zwei simultane Flash-Schnittstellen, die konfiguriert sind als

- Zwei OSPI-Flash-Schnittstellen

- oder HyperBus™- und OSPI1-Flash-Schnittstelle

- 2x 12-Bit-Analog-Digital-Wandler (ADC)

- Bis zu 4M Proben/s

- Acht gemultiplexte Analogeingänge

- 8x serielle Mehrkanal-Peripherieschnittstellen-Controller (McSPI)

- Zwei mit internen Anschlüssen

- Sechs mit externen Schnittstellen

- Universal-I/O-Pins (GPIO)

- Steuerschnittstellen

- 6x verbesserte hochauflösende Impulsbreitenmodulation (eHRPWM) Module

- Ein Enhanced Capture-Modul (eCAP)

- 3x Enhanced Quadrature Encoder Pulse-Modul (eQEP)

- Automotive-Schnittstellen

- 2× modulare Controller-Area-Network-Module (MCAN) mit vollständiger CAN-FD-Unterstützung

- Audio-Schnittstellen

- 3x serielle Mehrkanal-Audio-Anschlussmodule (McASP)

- Medien und Datenspeicherung

- 2× Multimedia Card™/ Secure Digital (MMC™/ SD) Schnittstellen

- Vereinfachtes Leistungsmanagement

- Vereinfachte Leistungssequenz mit vollständiger Unterstützung für Dual-Spannungs-I/O

- Integrierte LDOs reduzieren die Komplexität der Leistungslösung

- Integrierter SDIO-LDO für den automatischen Spannungsübergang für die SD-Schnittstelle

- Integrierte Power-On-Reset-Generierung (POR) reduziert die Komplexität der Leistungslösung

- Integrierter Spannungswächter für die funktionale Sicherheitsüberwachung

- Integrierter Stromversorgungs-Glitch-Detektor zur Erkennung von schnellen Stromversorgungs-Transienten

- Analog/Systemintegration

- Integrierte USB VBUS-Erkennung

- Ausfallsichere E/A für DDR-RESET

- Alle I/O-Pins sind während des Reset deaktiviert, um Bus-Konflikte zu vermeiden

- Standard-I/O-Impulse während des Reset deaktiviert, um Systemkonflikte zu vermeiden

- Unterstützt dynamische I/O-Pin-Mux-Konfigurationsänderung

- System-on-Chip(SoC)-Architektur

- Unterstützt primäres Booten von UART, I2C, OSPI, HyperBus, parallelem NOR Flash, SD oder eMMC™, USB, PCIe und Ethernet Schnittstellen

- 28 nm CMOS-Technologie

- 23 mm × 23 mm, Rastermaß von 0,8 mm, 784-Pin-FCBGA (ACD)

Applikationen

- Industrielle programmierbare Logik-Steuerungen (PLC)

- Fabrikautomatisierung mit Sicherheitsfunktionen

- Multiprotokoll-Feldbuskommunikation

- Industrie-PC

- Industrieroboter

- Mensch-Maschine-Schnittstelle (HMI)

- Netzinfrastruktur-Schutzrelais

- Robotermotorantriebe

Videos

Funktionales Blockdiagramm