Nexperia 74LVC8T595 Umsetzungs-Schieberegister

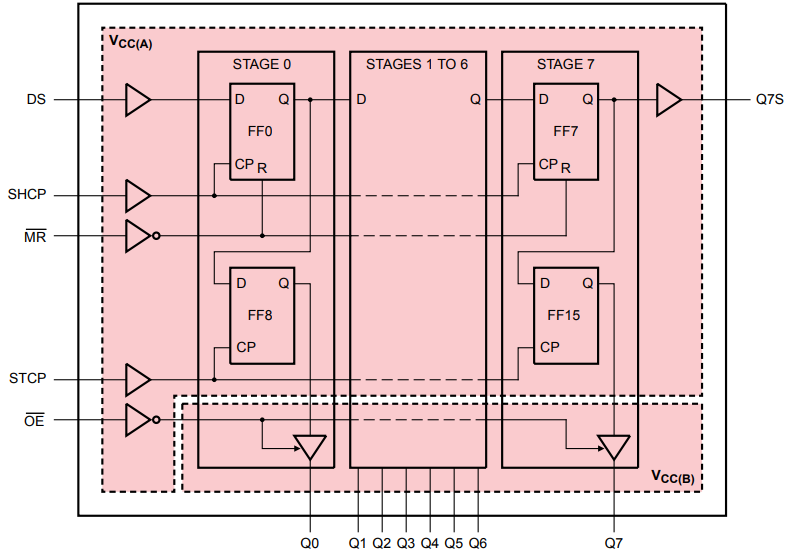

Die Umsetzungs-Schieberegister 74LVC8T595 von Nexperia sind Dual-Versorgungs-8-Bit-Schieberegister mit serieller Eingabe/serieller oder paralleler Ausgabe mit einem Speicherregister und dreistufigen Ausgängen. Diese stromsparenden CMOS-Lösungen sind vollständig spezifiziert von 1,1 V bis 5,5 V und eignen sich für die Verbindung von Niederspannungs-MCUs mit älteren Peripheriegeräten. Die 74LVC8T595 schieben und speichern Register, verfügen über separate Takte und Daten werden auf die positivgehenden Übergänge des SHCP-Eingangs geschoben. Die Daten im Schieberegister werden auf ein Speicherregister eines positiv-gehenden Übergangs des STCP-Eingangs übertragen. Wenn beide Takte miteinander verbunden werden, ist das Schieberegister stets einen Taktimpuls vor dem Speicherregister.Merkmale

- Großer Spannungsversorgungsbereich:

- VCC(A): 1,1 V bis 5,5 V

- VCC(B): 1,1 V bis 5,5 V

- Hohe Störfestigkeit

- Erfüllt alle JEDEC-Standards:

- JESD8-12A (1,1 V bis 1,3 V)

- JESD8-11A (1,4 V bis 1,6 V)

- JESD8-7 (1,65 V bis 1,95 V)

- JESD8-5 (2,3 V bis 2,7 V)

- JESD8C (3,0 V bis 3,6 V)

- JESD12-6 (4,5 V bis 5,5 V)

- ESD-Schutz:

- HBM ANSI/ESDA/JEDEC JS-001 Klasse 3A übertrifft 4.000 V

- CDM JESD22-C101E übertrifft 1.000 V

- Aussetz-Modus

- Latch-Up-Leistung übertrifft 100 mA gemäß JESD 78, Klasse II

- ±24 mA Ausgangstreiber (VCC(A) = VCC(B) = 3,0 V)

- Die Eingänge akzeptieren Spannungen bis zu 5,5 V

- Der IOFF-Schaltkreis bietet einen Betrieb im teilweisen Abschaltmodus

- Zahlreiche Gehäuseoptionen

- Spezifiziert von -40 °C bis +85 °C und von -40 °C bis +125 °C

Logik-Diagramm

Weitere Ressourcen

Veröffentlichungsdatum: 2018-05-08

| Aktualisiert: 2023-03-15