Analog Devices / Maxim Integrated DS2476 Deep Cover® Secure-Prozessor

Der Maxim DS2476 Deep Cover® Secure-Prozessor ist eine sichere ECDSA und HMAC SHA-256 Coprozessor-Ergänzung zum DS28C36. Der Coprozessor kann alle erforderlichen HMACs oder ECDSA Signaturen verarbeiten, um alle Vorgänge auf dem DS28C36 verarbeiten. Der DS2476 bietet eine Kerngruppe von Kryptografietools, die von integrierten asymmetrischen (ECC-P256) und symmetrischen (SHA-256) Sicherheitsfunktionen abgeleitet ist. Zusätzlich zu den Sicherheitsdiensten, die von den Krypto-Engines der Hardware implementiert werden, enthält die Ausrüstung einen FIPS/NIST Zufallszahlengenerator (True Random Number Generator, RNG). Das Gerät integriert auch einen gesicherten 8Kb-EEPROM, einen ausschließlich dekrementierbaren Zähler, zwei konfigurierbare GPIO-Kontakte und eine einzigartige 64-Bit ROM-Identifikationsnummer (ROM ID). Die ECC-Public-/Private-Key-Funktionen werden von der NIST-definierten P-256 Kurve betrieben. Diese Schlüssel umfassen eine FIPS 186-konforme ECDSA-Signaturerstellung und -verifizierung zur Unterstützung eines bidirektionalen asymmetrischen Key-Authentifizierungsmodells. Die geheimen SHA-256 Schlüsselfunktionen sind mit FIPS 180 konform und können flexibel entweder in ECDSA-Operationen oder unabhängig in mehreren HMAC-Funktionen verwendet werden.The Analog Devices DS2476 Deep Cover® Secure Processor is offered in a TDFN-6 package with an exposed pad for superior thermal performance.

Merkmale

- ECC-256 Compute Engine

- FIPS 186 ECDSA P256 Signature and Verification

- ECDH Key Exchange with Authentication Prevents Man-in-the-Middle Attacks

- ECDSA Authenticated R/W of Configurable Memory

- FIPS 180 SHA-256 Compute Engine

- HMAC

- SHA-256 OTP (One-Time Pad) Encrypted R/W of Configurable Memory Through ECDH Established Key

- Two GPIO Pins with Optional Authentication Control

- Open-Drain, 4mA/0.4V

- Optional SHA-256 or ECDSA Authenticated On/Off and State Read

- Optional ECDSA Certificate to Set On/Off after Multiblock Hash for Secure Boot

- RNG with NIST SP 800-90B Compliant Entropy Source with Function to Read Out

- Optional Chip Generated Pr/Pu Key Pairs for ECC Operations

- 17-Bit One-Time Settable, Nonvolatile Decrement-Only Counter with Authenticated Read

- 8Kbits of EEPROM for User Data, Keys, and Certificates

- Unique and Unalterable Factory Programmed 64-Bit Identification Number (ROM ID)

- Optional Input Data Component to Crypto and Key Operations

- I2C Communication, 100kHz and 400kHz

- Operating Range 3.3V ±10%, -40°C to +85°C

- TDFN-EP-6 Package

Applikationen

- Accessory and Peripheral Secure Authentication

- Controller

- IoT Node Crypto-Protection

- Parameters

- Secure Boot or Download of Firmware and/or System

- Secure Storage of Cryptographic Keys for a Host

Videos

Typical Application Circuit

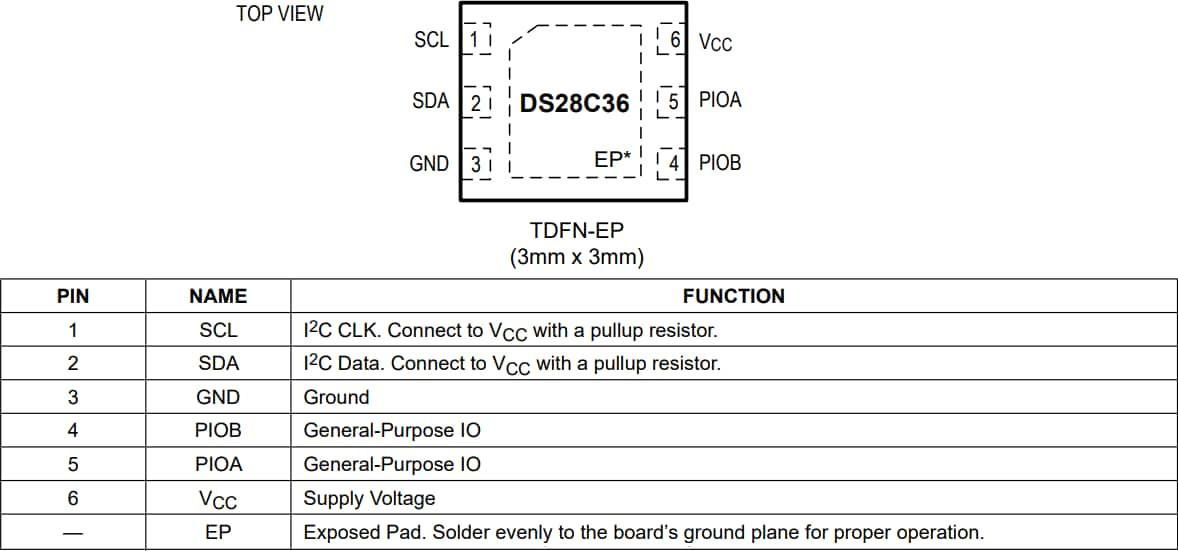

Pin Designations

Veröffentlichungsdatum: 2016-09-30

| Aktualisiert: 2023-04-12