Analog Devices Inc. AD9988 4T4R Direkter HF-Empfänger und -Sender

Der Analog Devices Inc. direkte HF-Empfänger und -Sender AD9988 4T4R ist ein hochintegrierter Baustein mit vier HF-Digital-Analog-Wandler(DAC)-Cores mit einer maximalen Abtastrate von 16-Bit und 12 GS/s sowie vier HF-Analog-Digital-Wandler(ADC)-Cores mit einer Rate von 12-Bit und 4 GS/s. Der AD9988 unterstützt vier Sender- und vier Empfängerkanäle mit einer 4T4R-Konfiguration.Der ADI AD9988 4T4R direkte HF-Empfänger und -Sender ist für TDD-Sender-Applikationen mit vier Antennen ausgelegt, bei denen der Empfängerpfad zwischen Empfänger- und Beobachtungsmodi geteilt wird. Die Phasenkohärenz wird aufrecht erhalten, während die GPIO-Pins konfiguriert und umgeschaltet werden können, um verschiedene Benutzermodi zu unterstützen. Das Bauteil bietet eine maximale Funkkanal-Bandbreite von 1,2 GHz in einer 4T4R-Konfiguration und eine Beispielauflösung von 16-Bit.

Der AD9988 verfügt über einen seriellen Datenport mit 16 Lanes (24,75 GBit/s JESD204C oder 15,5 GBit/s JESD204B), der bis zu acht Lanes pro Sende-/Empfangsstrecke ermöglicht, einen On-Chip-Taktmultiplikator und digitale Signalverarbeitungsfunktionen, die auf Multiband-Direktfunkanwendungen ausgerichtet sind.

Merkmale

- Flexibles, rekonfigurierbares gängiges Funkplattform-Design

- Sender-/Empfängerkanal-Bandbreite von bis zu 1,2 GHz (4T4R)

- HF-DAC/HF-ADC-HF-Frequenzbereich von bis zu 7,5 GHz

- On-Chip-PLL mit Multichip-Synchronisierung

- Option Externer RF-Takteingang

- Vielseitige digitale Funktionen

- Wählbare Interpolations- und Dezimationsfilter

- Konfigurierbare DDCs und DUCs

- 8 feine komplexe DUCs (FDUC) und 4 grobe komplexe DUCs (CDUC)

- 8 feine komplexe DDCs (FDDC) und 4 grobe komplexe DDCs (CDDC)

- FDUCs und FDDCs sind vollständig umgehbar

- 2 unabhängige 48-Bit-NCOs pro DUC oder DDC

- Programmierbarer 192-Tap-PFIR-Filter für Empfangsentzerrung

- Unterstützt vier verschiedene Profileinstellungen, die über GPIO geladen werden

- Unterstützung für Empfangs-AGC

- Schnelle Erkennung mit niedriger Latenz für eine schnelle AGC-Steuerung

- Signalüberwachung für langsame AGC-Steuerung

- Dedizierte AGC-Support-Pins

- Unterstützung für Sende-DPD

- Programmierbare Verzögerung und Gain pro Übertragungs-Datenpfad

- Grobe DDC-Verzögerungsanpassung für DPD-Beobachtungspfad

- Unterstützt reale oder komplexe digitale Daten (8-, 12-, 16-Bit)

- Hilfsfunktionen

- ADC-Takttreiber mit wählbaren Teilungsverhältnissen

- Nachgeschaltete Schutzschaltung für Leistungsverstärker

- On-Chip-Temperaturüberwachungseinheit

- Programmierbare GPIO-Pins unterstützen das Umschalten zwischen den Modi

- TDD-Stromsparoption und gemeinsame ADCs

- JESD204B- oder JESD204C-SERDES-Schnittstelle, 16 Leitungen bis zu 24,75 GBit/s

- 8 Lanes JESD204B/C Sender (JTx) und 8 Lanes JESD204B/C Empfänger (JRx)

- Unterstützt Unterklasse 1

- Unterstützt Multi-Gerät-Synchronisierung

- 324-Ball-BGA von 15 mm x 15 mm mit einem Rastermaß von 0,8 mm

Applikationen

- Drahtlose Kommunikationsinfrastruktur

- W-CDMA, LTE, LTE-A, massiver Mehrfacheingangs-Mehrfachausgang (MIMO)

- Punkt-zu-Punkt-Mikrowelle, E-Band und 5G-mmWave

- Breitband-Kommunikationssysteme

- DOCSIS 3.0+ Kabelmodem-Anschlusssystem (CMTS)

- Test- und Messsysteme für die Kommunikation

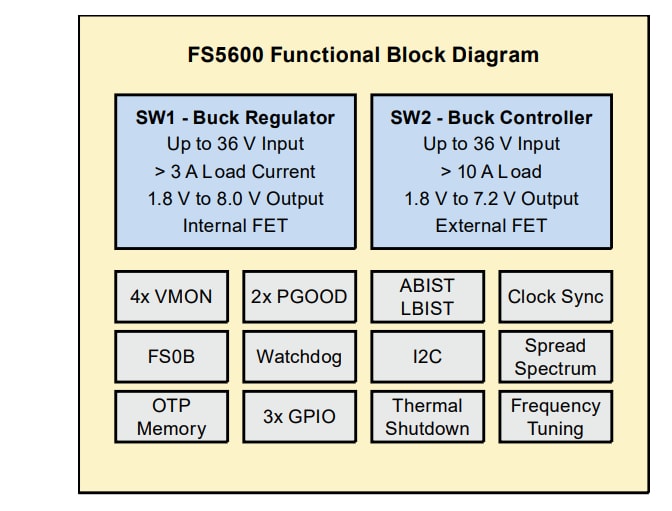

FUNKTIONALES BLOCKDIAGRAMM